Associate Professor

Department of Electrical & Computer EngineeringSan Diego State University

Research

My research work targets applications of machine learning and data mining to trustworthiness of ICs/systems, VLSI testing, and intelligent vehicles.

1. Trustworthy analog integrated circuits

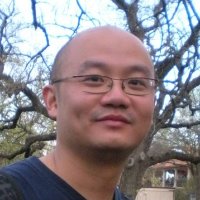

As semiconductor technology advances, analog integrated circuits (ICs) are becoming increasingly susceptible to a new and insidious threat: analog Aging Trojans (ATs). Unlike traditional malicious Trojans that directly compromise circuit functionality or introduce backdoor vulnerabilities, analog ATs operate covertly, exploiting the inherent physical degradation mechanisms present in analog components to induce accelerated aging effects. In this work, we show that maliciously introduced analog ATs can be efficiently detected using unsupervised machine learning models.

2. Ecological driving system for connected/automated vehicles

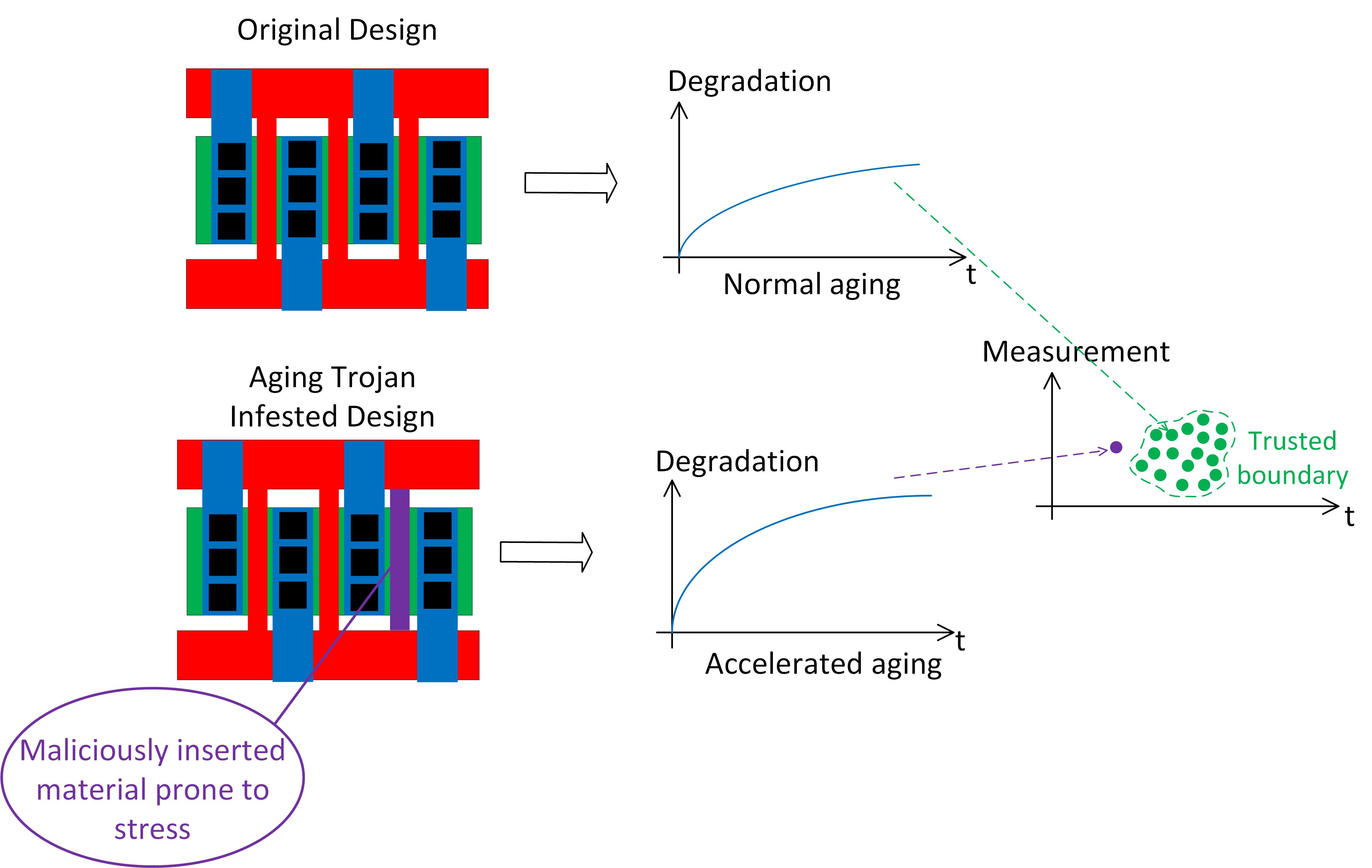

To improve a vehicle's fuel efficiency when operating on roadways, we develop an ecological driving system under the connected and automated vehicle (CAV) environment. The system includes three critical functions, including traffic state prediction, eco-driving speed control, and powertrain control implementation. According to the real-time traffic information obtained from vehicle-to-infrastructure and vehicle-to-vehicle communications, the embedded traffic state prediction model will estimate and predict the average speeds and densities of freeway subsections. Then our eco-driving speed control function is employed to minimize fuel consumption based on a two-stage hierarchical framework. Finally, the control parameters obtained from the speed control function will be forwarded to the powertrain control system for implementations.

3. Counterfeit IC detection and avoidance based on machine learning

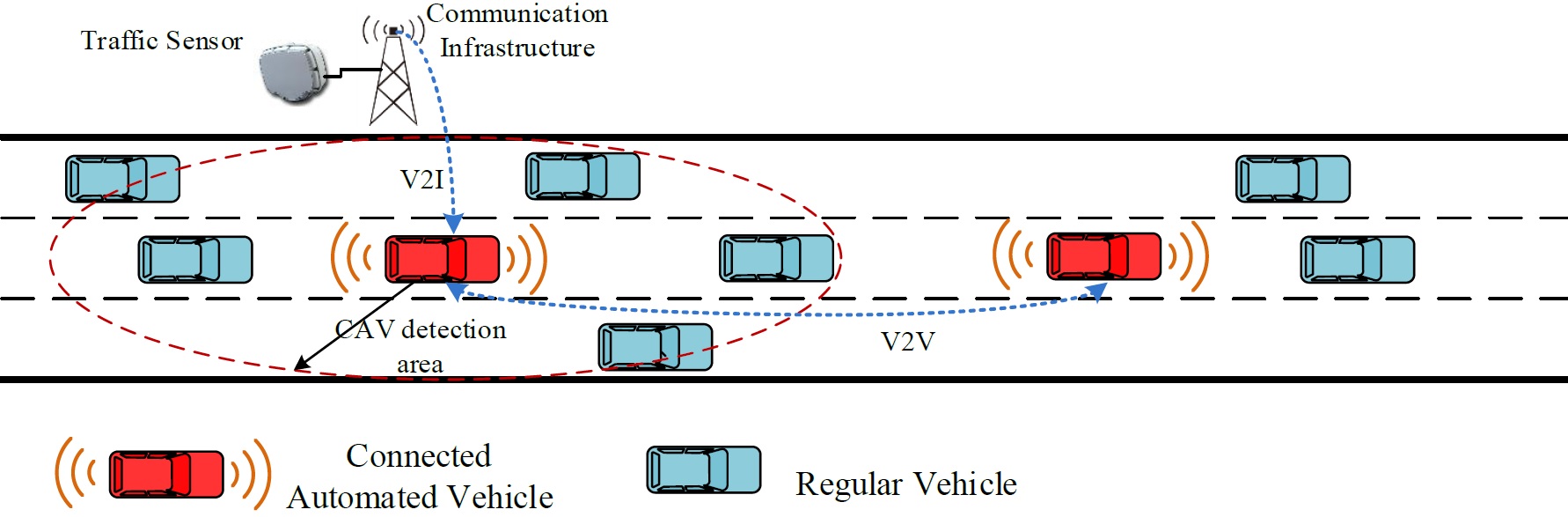

Counterfeit ICs, a major source of infection in the electronic component supply chain because of reliability and security issues, are impacting many industrial sectors, including computers, telecommunications, automotive electronics, and even military systems. The consequences, obviously, can be dramatic when critical systems begin to fail due to the use of counterfeit or low-quality components. The tools and technologies utilized by counterfeiters have become extremely sophisticated and well financed. In turn, this also calls for more sophisticated methods to detect counterfeit electronic parts that enter the market. We developed a statistical approach to distinguish recycled counterfeit ICs by training a one-class classifier using only brand new devices. The measurements used to build the classifier are typical test results from production Early Failure Rate analysis required to release most products, thus no additional costs in terms of design, test and area/power overhead are incurred to perform identification, and the method is demonstrated on actual IC measurements.

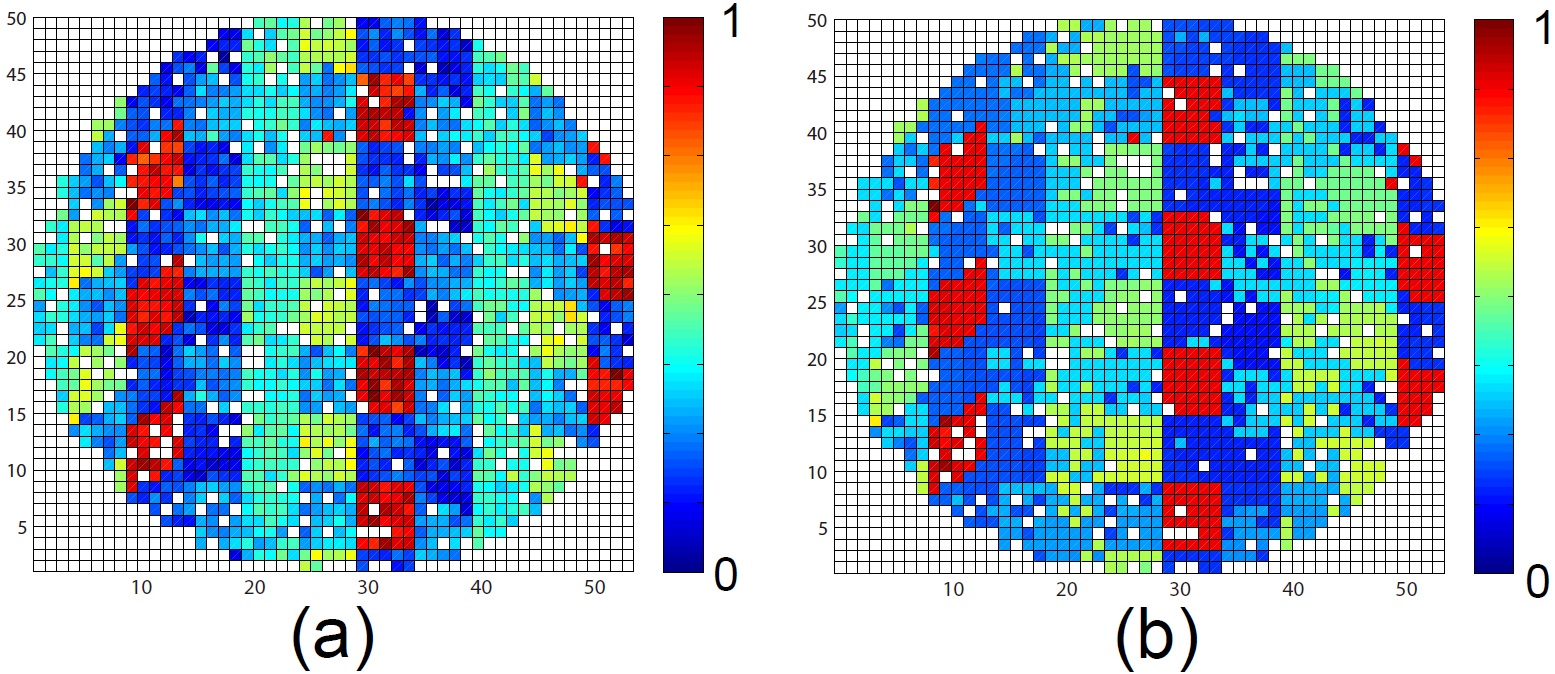

4. Specification test cost reduction of analog/RF ICs based on wafer-level spatial correlation models

Test cost reduction for analog/RF devices has been an ongoing topic of interest to the semiconductor manufacturing industry. Automated test equipment designed to collect parametric measurements, particularly at high frequencies, can be very costly. Together with lengthy set up and test times for certain measurements, these cause amortized test cost to comprise a high percentage of the total cost of manufacturing semiconductor devices. We investigated a spatial correlation modeling approach using Gaussian process models to enable extrapolation of performances via sparse sampling of probe test data. The proposed method performs an order of magnitude better than existing spatial sampling methods, while requiring an order of magnitude less time to construct the prediction models. The proposed methodology was validated on high-volume manufacturing data for more than 3,000 wafers.

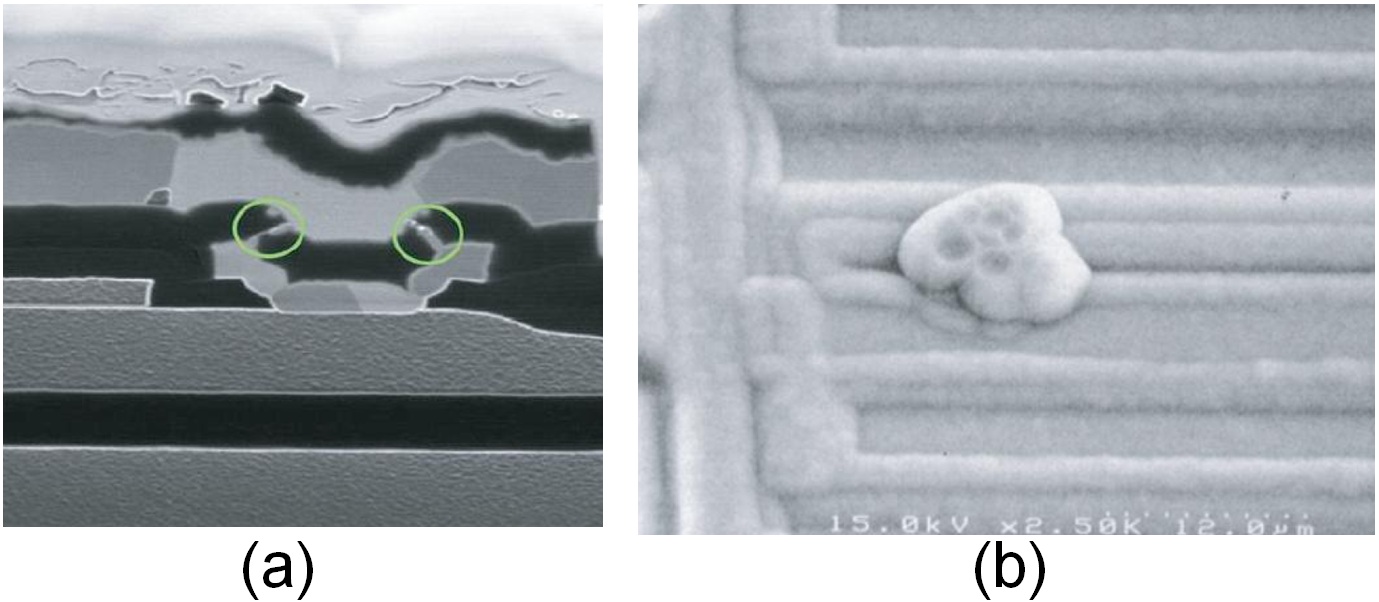

5. Fault modeling and diagnosis of analog/RF integrated circuits based on machine learning

Fault diagnosis is very useful at the design stage for debugging purposes, at high-volume manufacturing for obtaining feedback about the underlying fault mechanisms and improving the design and layout in future IC generations, and in cases where the IC is part of a larger safety-critical system (e.g. automotive, aerospace) for identifying the root-cause of failure and for applying corrective actions that will prevent failure reoccurrence and, thereby, will expand the safety features. We developed a methodology for fault modeling and fault diagnosis of analog circuits based on machine learning. A defect filter is used to recognize the type of fault (parametric or catastrophic), inverse regression functions are used to locate and predict the values of parametric faults, and multi-class classifiers are used to list catastrophic faults according to their likelihood of occurrence. The methodology was demonstrated on both simulation and high-volume manufacturing data showing excellent overall diagnosis rate.

©2025